# **FEATURES**

- True 125MHz retrigger rate

- Pin-compatible with Bt605

- 15ps delay resolution

- Less than ± 1 LSB timing accuracy

- Differential TRIGGER and delay WRITE inputs

- Delay spans from 4 to 40ns

- Compatible with 10KH ECL logic

- Lower power dissipation 350mW typical

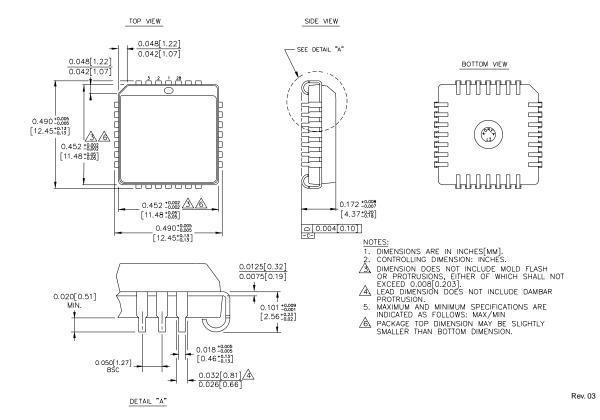

- Available in 28-pin plastic (PLCC) or metal (MLCC) J-lead package

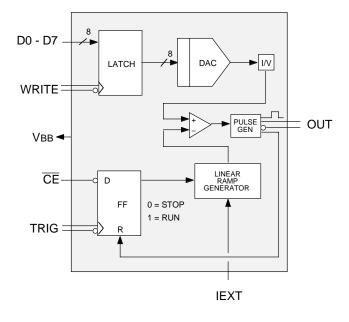

# **BLOCK DIAGRAM**

## **DESCRIPTION**

Micrel-Synergy's SY605 is an ECL-compatible timing vernier (delay generator) whose time delay is programmed via an 8-bit code which is loaded via an independent "WRITE" input. The SY605 is fabricated in Micrel-Synergy's proprietary ASSET $^{\text{TM}}$  bipolar process.

This device can be retriggered at speeds up to 125MHz, with a delay span as short as 4ns. At minimum span, the resolution is 4ns/255 = 15.7ps per step. The delay span is externally adjustable up to 40ns. The SY605 employs differential TRIGGER and WRITE inputs, and produces a differential OUTPUT pulse; all other control signals are single-ended ECL. Edge delay is specified by an 8-bit input which is loaded into the device with the WRITE signal. The output pulse width will typically be 3.5ns.

The SY605 is commonly used in Automatic Test Equipment to provide precise timing edge placement; it is also found in many instrumentation and communications applications.

Micrel-Synergy's circuit design techniques coupled with ASSET™ technology result in not only ultra-fast performance, but allow device operation at lower power dissipation than competing technologies. Outstanding reliability is achieved in volume production.

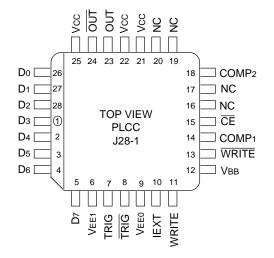

## PIN CONFIGURATION

## PIN DESCRIPTION

#### D0 - D7

Data input pins (ECL compatible). On the falling edge of WRITE, D0 - D7 are latched into the DAC input register. D0 is the LSB. These inputs specify the amount of delay from the rising edge of TRIG to the output pulse.

#### WRITE, WRITE

Differential write inputs (ECL compatible). These inputs control the parallel data input latch. When WRITE is a logical one, the data latch is transparent. Data is latched on the falling edge of WRITE. A single-ended write may be used by connecting  $\overline{\text{WRITE}}$  to VBB.

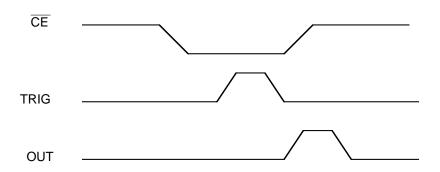

#### CE

Chip enable input (ECL compatible).  $\overline{\text{CE}}$  must be a logical zero on the rising edge of TRIG to enable the device to respond to the trigger. If  $\overline{\text{CE}}$  is floating, the trigger will always be enabled.

## TRIG, TRIG

Differential trigger inputs (ECL compatible). The rising edge of TRIG is used to trigger the delay cycle if  $\overline{CE}$  is a logical zero. If  $\overline{CE}$  is a logical one, no operation occurs. It is recommended that triggering be performed with differential inputs.

### OUT, OUT

Differential outputs (ECL compatible).

#### **IEXT**

Current reference pin. The amount of current sourced into this pin determines the span of output delay. The voltage at IEXT is typically –1.25V.

#### COMP1, COMP2

Compensation pins. A  $0.1\mu F$  ceramic capacitor must be connected between COMP1 and VEE0, and COMP2 and VEE0 (see Figure 3).

#### VEE

Device power. All VEE pins must be connected.

#### Vcc

Device ground. All Vcc pins must be connected together.

#### **V**RR

A -1.36V (typical) output.

#### **FUNCTIONAL DESCRIPTION**

The output pulse generation cycle begins with the arrival of TRIG shown in **Figure 1**. The DAC values are latched by the rising edge of WRITE. Then, when TRIG transitions to a high and  $\overline{CE}$  is low the linear ramp is initiated.

When the ramp level reaches that of the DAC, the comparator initiates the pulse generator to produce an output pulse resets the ramp and the cycle is ready to begin again.

Figure 1.

# ABSOLUTE MAXIMUM RATING(1)

| Symbol | Parameter                           | Value        | Unit |

|--------|-------------------------------------|--------------|------|

| VEE    | Power Supply (Vcc = 0V)             | −8 to 0      | V    |

| Vı     | Input Voltage (Vcc = 0V)            | 0 to VEE     | V    |

| Іоит   | Output Current — Continuous — Surge | 50<br>100    | mA   |

| TA     | Operating Temperature Range         | 0 to +85     | °C   |

| VEE    | Operating Range <sup>(2)</sup>      | −5.7 to −4.2 | V    |

#### NOTES:

- 1. Beyond which device life may be impaired.

- 2. Parametric values specified at 10E Series: -4.75V to -5.5V

# **DC CHARACTERISTICS**

|              |                                                                                                             | TA = +0°C                                    |                                              | TA = +25°C                                   |                                              |                                              | TA = +70°C                                   |                                              |                                              |                                              |                            |

|--------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------|

| Symbol       | Parameter                                                                                                   | Min.                                         | Тур.                                         | Max.                                         | MIn.                                         | Тур.                                         | Max.                                         | Min.                                         | Тур.                                         | Max.                                         | Unit                       |

| ViH          | Input HIGH Voltage (10K)                                                                                    | -1170                                        | _                                            | -840                                         | -1130                                        | _                                            | -810                                         | -1070                                        | _                                            | -735                                         | mV                         |

| VIL          | Input LOW Voltage (10K)                                                                                     | -1950                                        | _                                            | -1480                                        | -1950                                        | _                                            | -1480                                        | -1950                                        | _                                            | -1450                                        | mV                         |

| Vон          | Output HIGH Voltage (10K)                                                                                   | -1020                                        | -975                                         | -840                                         | -980                                         | -920                                         | -810                                         | -920                                         | -850                                         | -735                                         | mV                         |

| Vol          | Output LOW Voltage (10K)                                                                                    | -1950                                        | -1755                                        | -1630                                        | -1950                                        | -1750                                        | -1630                                        | -1950                                        | -1720                                        | -1600                                        | mV                         |

| IIH<br>IIH   | Input High Current (Vin = VIH max) TRIG, TRIG                                                               | _                                            | 100<br>100                                   | 150<br>150                                   | _                                            | 100<br>100                                   | 150<br>150                                   | _                                            | 100<br>100                                   | 150<br>150                                   | μA<br>μA                   |

| lil<br>lil   | Input Low Current (Vin = VIL min) TRIG, TRIG                                                                | _                                            | 100<br>100                                   | 150<br>150                                   | _                                            | 100<br>100                                   | 150<br>150                                   | _<br>_                                       | 100<br>100                                   | 150<br>150                                   | μA<br>μA                   |

| DL<br>IL     | Output Delay Spans Differential Linearity Error** Integral Linearity Error**                                |                                              | ±0.84<br>±1.16                               | ±0.9<br>±1.25                                |                                              | ±0.84<br>±0.89                               | ±0.9<br>±1.0                                 | _                                            | ±0.84<br>±0.89                               | ±0.9<br>±1.0                                 | LSB                        |

| Vвв          | Vвв Output Voltage                                                                                          | -1.44                                        | _                                            | -1.25                                        | -1.44                                        | -1.35                                        | -1.25                                        | -1.44                                        | _                                            | -1.25                                        | V                          |

| <b>I</b> EXT | IEXT for Tspans Tspan = 4ns Tspan = 5ns Tspan = 10ns Tspan = 15ns Tspan = 20ns Tspan = 30ns                 | 1.80<br>1.45<br>0.70<br>0.45<br>0.34<br>0.20 | 2.38<br>1.85<br>0.93<br>0.62<br>0.46<br>0.30 | 2.80<br>2.40<br>1.20<br>0.80<br>0.60<br>0.40 | 1.80<br>1.45<br>0.70<br>0.45<br>0.34<br>0.20 | 2.38<br>1.85<br>0.93<br>0.62<br>0.46<br>0.30 | 2.80<br>2.40<br>1.20<br>0.80<br>0.60<br>0.40 | 1.80<br>1.45<br>0.70<br>0.45<br>0.34<br>0.20 | 2.38<br>1.85<br>0.93<br>0.62<br>0.46<br>0.30 | 2.80<br>2.40<br>1.20<br>0.80<br>0.60<br>0.40 | mA<br>mA<br>mA<br>mA<br>mA |

|              | Tspan with IEXT = 1.8 mA<br>(Tspan = Tmax - Tmin)                                                           | 4.1                                          | _                                            | 6.5                                          | 4.1                                          |                                              | 6.5                                          | 4.1                                          | _                                            | 6.5                                          | ns                         |

| Tmin         | Minimum Delay Time* Data = 00, Tspan = 5ns Tspan = 10ns Tspan = 15ns Tspan = 20ns Tspan = 25ns Tspan = 30ns |                                              | 2.8<br>3.4<br>4.0<br>4.6<br>5.2<br>5.8       | 3.8<br>4.9<br>6.0<br>7.1<br>8.2<br>9.3       |                                              | 2.8<br>3.4<br>4.0<br>4.6<br>5.2<br>5.8       | 3.8<br>4.9<br>6.0<br>7.1<br>8.2<br>9.3       | _<br>_<br>_<br>_<br>_                        | 2.8<br>3.4<br>4.0<br>4.6<br>5.2<br>5.8       | 3.8<br>4.9<br>6.0<br>7.1<br>8.2<br>9.3       | ns<br>ns<br>ns<br>ns<br>ns |

| lee          | VEE Supply Current                                                                                          | _                                            | _                                            | 100                                          |                                              | 70                                           | 100                                          | _                                            | _                                            | 100                                          | mA                         |

#### NOTE:

<sup>1. 10</sup>K series circuits are designed to meet the DC specifications shown in the table after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse air flow greater than 500 lfpm is maintained. Outputs are terminated through a 50Ω resistor to -2.0 volts.

# **AC CHARACTERISTICS**

ECL input values are -0.9 to -1.7V, with input rise/fall times  $\leq$  2ns, measured between the 20% and 80% points. Timing reference points at 50% for inputs and outputs. OUT and  $\overline{\text{OUT}}$  loading with  $50\Omega$

to -2.0V. Typical values are based on nominal temperature, i.e., and nominal voltage, i.e., - 5.2V.

|                   |                                                                                                           | TA = +0°C         |              | TA = +25°C  |                   |              | TA = +70°C  |                   |              |                 |                        |

|-------------------|-----------------------------------------------------------------------------------------------------------|-------------------|--------------|-------------|-------------------|--------------|-------------|-------------------|--------------|-----------------|------------------------|

| Symbol            | Parameter                                                                                                 | Min.              | Тур.         | Max.        | Min.              | Тур.         | Max.        | Min.              | Тур.         | Max.            | Unit                   |

| fMAX              | Trigger Rate <sup>(1)</sup>                                                                               | _                 | _            | 125         | _                 | _            | 125         | _                 | _            | 125             | MHz                    |

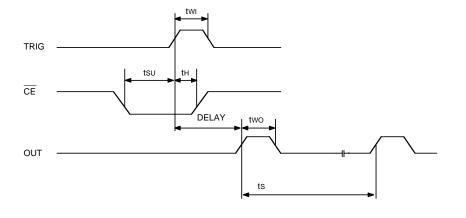

| twı               | Trigger Width High                                                                                        | 2.0               | 1.0          | _           | 2.0               | 1.0          | _           | 2.0               | 1.0          | -               | ns                     |

| two<br>ts         | Output Pulse Width High Time Output Pulse Rise/Fall Time (20/80%) Output Pulse Spacing Span = 4ns @ 1 LSB | 2.5<br>—<br>8.0   | 3.5<br>550   | 4.5<br>750  | 2.5<br>—<br>8.0   | 3.5<br>550   | 4.5<br>750  | 2.5<br>—<br>8.0   | 3.5<br>550   | 4.5<br>750<br>— | ns<br>ps<br>ns         |

|                   | Minimum Delay Time vs. Tspan Δ T00 / ns (Tspan = 5 to 10ns)                                               | _                 | 125          | 220         | _                 | 125          | 220         | _                 | 125          | 220             | ps/ns                  |

| 1 LSB<br>1 LSB    | Output Delay Tspan (Tspan = Tmax - Tmin) Resolution (Tspan / 225) Tempo (5ns Span)                        | 4.0<br>15.7       |              | 40<br>157   | 4.0<br>15.7       | -            | 40<br>157   | 4.0<br>15.7       | _            | 40<br>157       | ns<br>ns<br>ps         |

|                   | Δ Tspan /°C Δ Tmin /°C Power Supply Rejection (Data = 0-FF HEX, Tspan = 5ns)                              | _<br>_<br>_       | 2<br>2<br>60 | _<br>_<br>_ | _<br>_<br>_       | 2<br>2<br>60 | _<br>_<br>_ | _<br>_<br>_       | 2<br>2<br>60 | _<br>_<br>_     | ps/°C<br>ps/°C<br>ps/V |

| ts<br>tH          | CE Setup Time CE Hold Time                                                                                | 2.0<br>1.5        |              | _           | 2.0<br>1.5        |              | _           | 2.0<br>1.5        | _            |                 | ns<br>ns               |

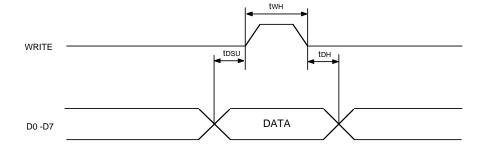

| twh<br>tds<br>tdh | WRITE Pulse Width High Time<br>D0 - D7 Setup Time<br>D0 - D7 Hold Time                                    | 2.0<br>1.0<br>1.5 |              |             | 2.0<br>1.0<br>1.5 |              |             | 2.0<br>1.0<br>1.5 | _<br>_<br>_  |                 | ns<br>ns<br>ns         |

#### NOTE:

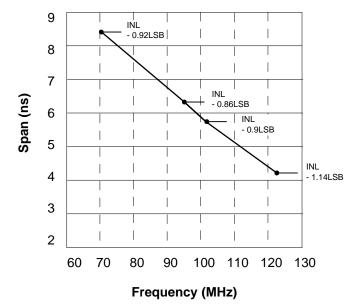

## **Maximum Tspan and Trigger Rates**

| Maximum Tspan (ns) Maintaining Linearity | Minimum Trigger<br>Periods (ns) |

|------------------------------------------|---------------------------------|

| of ±1 LSB                                |                                 |

| 4.0                                      | 8.0                             |

| 5.1                                      | 10.0                            |

| 5.8                                      | 11.1                            |

| 6.75                                     | 12.5                            |

| 8.1                                      | 14.3                            |

| 9.9                                      | 16.6                            |

| 12.0                                     | 20.0                            |

| 15.5                                     | 25.0                            |

| 22.0                                     | 33.3                            |

The information in this table is guaranteed but not 100% production tested.

See Figure 2 for a graphical representation.

<sup>1.</sup> See chart below:

# TIMING DIAGRAMS

± 1 LSB Span vs. Trigger Rates

Figure 2.

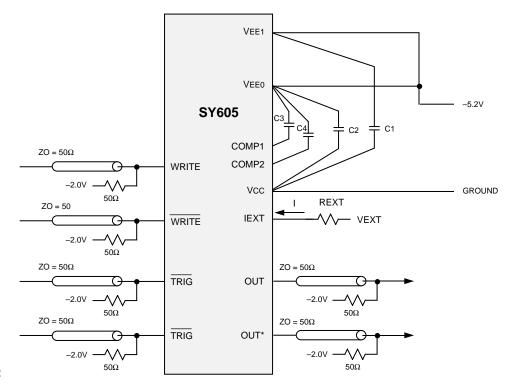

# **APPLICATION DIAGRAM**

**REXT Calculation:**

REXT = (VEXT + 1.25V)/IEXT

# For Example:

If Tspan is around 15ns, then IEXT is around 0.6mA, (see DC Characteristic Table) and assume IEXT pin is tied to Vcc with the resistor.

REXT = 0 + 1.25V/0.6mA

= 2.08 K ohm

| Location | Description                                        | Vendor Part Number       |

|----------|----------------------------------------------------|--------------------------|

| C1-C4    | 0.1μF ceramic capacitor                            | Erie RPE112Z5U104M50V    |

| REXT     | 1% metal film resistor (selected for proper Tspan) | CB301210<br>Dale CMF-55C |

#### NOTE:

The vendor numbers above are listed only as a guide. Substitution of devices with similar characteristics will not affect the performance of the SY605. All devices should be as close as possible to the SY605.

Figure 3. Typical Connection Diagram and Parts List.

# PRODUCT ORDERING CODE

| Ordering<br>Code | Package<br>Type | Operating<br>Range |

|------------------|-----------------|--------------------|

| SY605JC          | J28-1           | Commercial         |

| SY605JCTR        | J28-1           | Commercial         |

# 28 LEAD PLCC (J28-1)

7